# iW- SD Memory Slave Demo User Manual

# **Table of Contents**

| 1. INTRODUCTION |                                            | 5  |

|-----------------|--------------------------------------------|----|

| 1.1             | Purpose                                    | 5  |

| 1.2             | SCOPE                                      |    |

| 1.3             | ACRONYMS AND ABBREVIATIONS                 | 5  |

| 1.4             | Overview                                   | 6  |

| 1.5             | DEMO BOARD AND ACCESSORIES                 | 6  |

| 1.6             | SOFTWARE REQUIREMENTS                      | 6  |

| 1.7             | PLATFORM HIGHLIGHTS                        | 6  |

| 2. IV           | V- SD MEMORY SLAVE DEMO BOARD              | 8  |

| 2.1             | BLOCK DIAGRAM                              | 8  |

| 2.2             |                                            |    |

| 2.2             | 2.1 SD interface                           |    |

|                 | 2.2 Oscillator                             |    |

| 2.2             | 2.3 UART interface                         | 8  |

|                 | 2.4 JTAG connector                         |    |

|                 | 2.5 Expansion connectors                   |    |

|                 | PIN OUTS OF IW- SD MEMORY SLAVE            |    |

| 2.4             | PIN OUTS FOR EXPANSION CONNECTOR FROM FPGA |    |

| 2.5             | PIN OUTS OF TEST LEDS                      | 10 |

| 3. RI           | EFERENCE DESIGN DETAILS                    | 11 |

| 4. O            | UICK START                                 | 12 |

# **List of Figures**

| Figure 1: Detailed view of iW-SD Memory Slave demo Board  | 6  |

|-----------------------------------------------------------|----|

| Figure 2 : Block diagram of iW-SD Memory Slave demo board |    |

| Figure 3: iW- SD memory slave reference design            |    |

| Figure 4: SD Memory Slave IP test setup                   |    |

| Figure 5: Card detection prints                           |    |

| Figure 6: Write operation prints                          |    |

| Figure 7: Read operation Prints                           | 14 |

# **List of Tables**

| Table 1 : Acronyms & Abbreviations                  | 5  |

|-----------------------------------------------------|----|

| Table 2 : Pin outs of iW- SD memory slave           |    |

| Table 3: Pin outs for Expansion connector from FPGA |    |

| Table 4 · Pin outs of LEDs                          | 10 |

## 1. Introduction

### 1.1 Purpose

The purpose of this document is to explain the procedure to power-on and setting up the working environment of iW-SD Memory Slave demo board and method to test the write and read operations.

### 1.2 Scope

This document describes the Hardware connection procedure to power-on, inserting SD Memory slave demo board. This document also helps to perform the write and read tests to verify the working of iW-SD Memory slave IP.

### 1.3 Acronyms and Abbreviations

**Table 1: Acronyms & Abbreviations**

| Term | Meaning                                     |

|------|---------------------------------------------|

| FPGA | Field Programmable Gate Array               |

| GPIO | General purpose Input/output                |

| LED  | Light Emitting Diodes                       |

| MMC  | Multi-Media Card                            |

| OS   | Operating System                            |

| PC   | Personal Computer                           |

| SD   | Secure Digital                              |

| UART | Universal Asynchronous Receiver/Transmitter |

| USB  | Universal Serial Bus                        |

#### 1.4 Overview

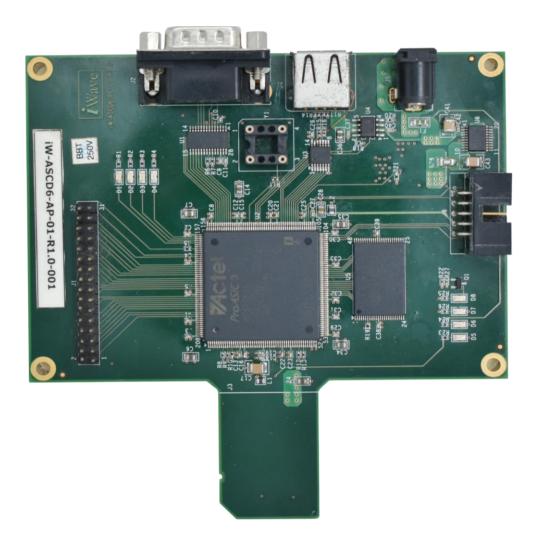

Figure 1: Detailed view of iW-SD Memory Slave demo Board

The iW-SD slave demo board can be used to evaluate iW-SD memory slave IP. The demo board also enables any designers seeking a development platform to validate their bridge cores. This versatility provides an ability to work with the SD bus and act as a useful bridge for target devices which require access to standard buses like UART, USB etc.

The demo board comes preconfigured with an iW-SD memory Slave reference design. Currently SD Memory Slave have been tested and proven using this demo board in Ubuntu 12.04 LTS version.

#### 1.5 Demo Board and accessories

• iW-SD Memory Slave demo board

### 1.6 Software Requirements

- A Laptop with SD 2.0 slot with Ubuntu OS installed

- Ubuntu 12.04 LTS Live CD if the Laptop is not having the Ubuntu OS installed

#### 1.7 Platform highlights

The iW-SD Memory Slave demo board consists of the following components.

- General

- o Actel Proasic3 (A3P250-PQG 208).

- 18.432 MHz Clock crystal oscillator.

- o UART transceiver (MAX3241).

- o 2 power LED outputs and 4 test LED outputs

- Connectors and interfaces:

- SD interface

- o RS-232 serial port

- o FPGA I/O signals through Expansion Connectors.

## 2. iW-SD Memory Slave Demo board

### 2.1 Block Diagram

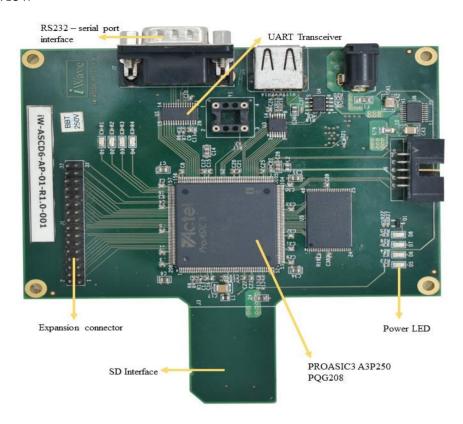

Figure 2: Block diagram of iW-SD Memory Slave demo board

### 2.2 Description

#### 2.2.1 SD interface

Physical bus interface takes care of the Command and data bus interface. This interface connects the SD host and FPGA and enables the communication between them. This interface is responsible for the transfer of the data between the FPGA in which the SD memory slave is implemented and SD host.

#### 2.2.2 Oscillator

Clock crystal oscillates at 18.432MHz which will be used as the system clock

#### 2.2.3 UART interface

This is optional Interface which will not be used for the SD memory slave IP demo. The UART (Universal Asynchronous Receiver/Transmitter) provides serial communication capabilities, which allow communication with modem or other external devices, like another computer using a serial cable via UART transceiver (MAX3241) and RS232 protocol.

#### 2.2.4 JTAG connector

Flashpro3 JTAG chain interface connected on this JTAG connector is used to program the FPGA by loading the programming files (PDB).

#### 2.2.5 Expansion connectors

Headers 16x2 are used for debugging on board FPGA signals.

## 2.3 Pin outs of iW-SD memory Slave

The pin outs of iW-SD Memory slave is as shown in the table below:

Table 2: Pin outs of iW-SD memory slave

| iW- SD Memory Slave<br>PINS | A3P250 –PQG 208<br>FPGA PIN |

|-----------------------------|-----------------------------|

|                             | numbers                     |

| sys_rst_n_i                 | 133                         |

| sys_clk_i                   | 136                         |

| sd_clk_i                    | 30                          |

| sd_cmd_io                   | 12                          |

| sd_data_io[0]               | 44                          |

| sd_data_io[1]               | 46                          |

| sd_data_io [2]              | 8                           |

| sd_data_io[3]               | 10                          |

## 2.4 Pin outs for Expansion connector from FPGA

Table 3: Pin outs for Expansion connector from FPGA

| Expansion connector<br>Pins | A3P250 PQG 208<br>FPGA pin numbers | Expansion connector Pins | A3P250 PQG 208<br>FPGA pin numbers |

|-----------------------------|------------------------------------|--------------------------|------------------------------------|

| PIN1                        | N/A (Vcc)                          | PIN17                    | 182                                |

| PIN2                        | N/A(Vcc)                           | PIN18                    | N/A                                |

| PIN3                        | 197                                | PIN19                    | 180                                |

| PIN4                        | 198                                | PIN20                    | 181                                |

| PIN5                        | 196                                | PIN21                    | 177                                |

| PIN6                        | N/A                                | PIN22                    | 179                                |

| PIN7                        | 193                                | PIN23                    | N/A                                |

| PIN8                        | 194                                | PIN24                    | 176                                |

| PIN9                        | 191                                | PIN25                    | 174                                |

| PIN10                       | 192                                | PIN26                    | 175                                |

| PIN11                       | N/A                                | PIN27                    | 172                                |

| PIN12                       | 190                                | PIN28                    | 173                                |

| PIN13                       | 188                                | PIN29                    | 168                                |

| PIN14                       | 189                                | PIN30                    | N/A                                |

| PIN15                       | 183                                | PIN31                    | 167                                |

| PIN16                       | 184                                | PIN32                    | 164                                |

## 2.5 Pin outs of Test LEDs

These LEDs are mounted on the board. But, the FPGA logic has not been implemented to control these LEDs. So, even if the board is powered ON, these LEDs will not glow.

**Table 4: Pin outs of LEDs**

| LED PINS | A3P250 –PQG 208 FPGA<br>PIN numbers |

|----------|-------------------------------------|

| D1       | 161                                 |

| D2       | 160                                 |

| D3       | 159                                 |

| D4       | 158                                 |

## 3. Reference Design Details

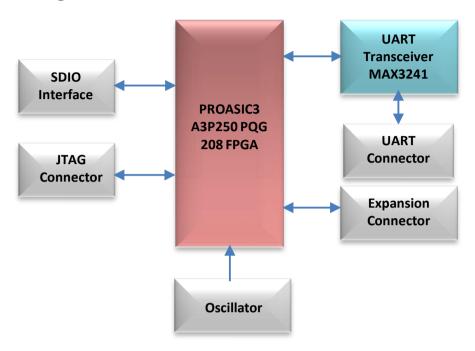

The SD memory slave reference design consists of mainly 2 parts, one is the SD memory slave IP and other is the 2KB user application. One side of the IP will be driven by the SD host and 2KB user application drives the other side. The data written from the SD in case of the write operation will be stored in the 2K RAM instantiated in the user application. During read, data will be read from the same as passed to the SD host.

Figure 3: iW-SD memory slave reference design

SD memory slave demo board is designed with Actel Proasic3 device (A3P250-PQG 208), which contains 8 RAM blocks. Out of these 8 blocks, the IP itself consumes 4 blocks for write and read buffer implementation and leaving rest 4 blocks for user application. So the user application memory is limited to 2KB due to the limitation of RAM blocks in the device.

The IP can be configured as standard capacity card as well as the high capacity card. User can configure the IP for higher size depending on the user memory availability.

## 4. Quick Start

### 4.1 Ubuntu Live session user setup

- Insert the CD in Laptop and reboot the system. Press F9 (Multi boot selection menu) while loading the OS.

- A boot menu appears. Select "CD/DVD ROM Drive" in the menu and press enter key.

- Select "English" as language and press enter if language menu appears on the screen.

- Select "Install Ubuntu" option using direction keys and press enter key if installation menu appears. This will load Ubuntu in to laptop.

- After loading the Ubuntu, Quit the installation if Installation menu appears on the Laptop screen.

- Ubuntu Live session user desktop will appear on the laptop screen.

### 4.2 Testing Procedure

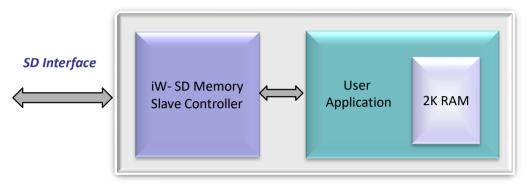

❖ **Test Setup:** The following figure shows the SD memory slave demo board connected to the Laptop where Ubuntu is installed. When the card is inserted to the SD slot the power LEDs will glow as shown in the figure below.

Figure 4: SD Memory Slave IP test setup

#### **A** Card Insertion Test:

Insert the Demo board in to the Laptop (Running with Ubuntu) SD slot. The prints can be checked in terminal window by giving "*dmesg*" command. The terminal print is as shown in below figure.

```

user@user-Presario-V3700-Notebook-PC:~$ dmesg

[ 2634.652369] mmc0: card 0001 removed

[ 2636.363045] mmc0: new SD card at address 0001

[ 2636.363463] mmcblk0: mmc0:0001 SDMEM 2.00 KiB

[ 2636.366652] Dev mmcblk0: unable to read RDB block 4

[ 2636.366833] mmcblk0: unable to read partition table

[ 2636.366843] mmcblk0: partition table beyond EOD, truncated user@user-Presario-V3700-Notebook-PC:~$

```

Figure 5: Card detection prints

This indicates that 2KB card is detected successfully.

#### **\*** Write Operation Test:

The write operation can be tested using the standard "dd" application. The write operation indicates the data from the SD host of Linux PC will be written to the SD memory implemented in FPGA.

Since the programmed SD memory Slave reference design is implemented with 2KB memory, maximum 2KB data can be written. The write operation can be done using the command "sudo dd of=<path of detected mmcblk> iflag=direct bs=<block legth> count=<number of blocks> if=/<path for input file>"

For example: "sudo dd of=/dev/mmcblk0 iflag=direct bs=512 count=4 of=/home/user/Desktop/test.txt"

This operation writes the test.txt file in the desktop to the SD memory implemented in FPGA. Here "bs=512" indicates the 512 block length and "count=4" indicates number of blocks for operation is of 4

Following figure shows the prints during the write operation.

```

user@user-Presario-V3700-Notebook-PC:~$

user@user-Presario-V3700-Notebook-PC:~$ sudo dd of=/dev/mmcblk0 iflag=direct bs=512 count=4 if=/home/user/Desktop/test.txt

4+0 records in

4+0 records out

2048 bytes (2.0 kB) copied, 0.00460073 s, 445 kB/s

user@user-Presario-V3700-Notebook-PC:~$

```

Figure 6: Write operation prints

#### **Read Operation Test:**

The read operation also can be tested using the standard "dd" application. The read operation indicates the data from SD memory implemented in FPGA will be read and written to SD host of Linux PC.

Since the programmed SD memory Slave reference design is implemented with 2KB memory, maximum 2KB data can be read. The read operation can be done using the command "sudo dd if=<path of detected mmcblk> iflag=direct bs=<block legth> count=<number of blocks> of=/<path for output file>"

For example: "sudo dd if=/dev/mmcblk0 iflag=direct bs=512 count=4 if=/home/user/Desktop/test\_read.txt"

This operation reads the data from the SD memory slave and writes the read data to the test\_read.txt file which will be saved in the Desktop. Here "bs=512" indicates the 512 block length and "count=4" indicates number of blocks for operation is of 4 Following figure shows the prints during the read operation.

```

user@user-Presario-V3700-Notebook-PC:~$

user@user-Presario-V3700-Notebook-PC:~$ sudo dd if=/dev/mmcblk0 iflag=direct bs=512 count=4 of=/home/user/Desktop/test_read.txt

4+0 records in

4+0 records out

2048 bytes (2.0 kB) copied, 0.000901232 s, 2.3 MB/s

user@user-Presario-V3700-Notebook-PC:~$

```

Figure 7: Read operation Prints