# **FPGA IP CORE**

# iW PCIe to SD/MMC Bridge IP

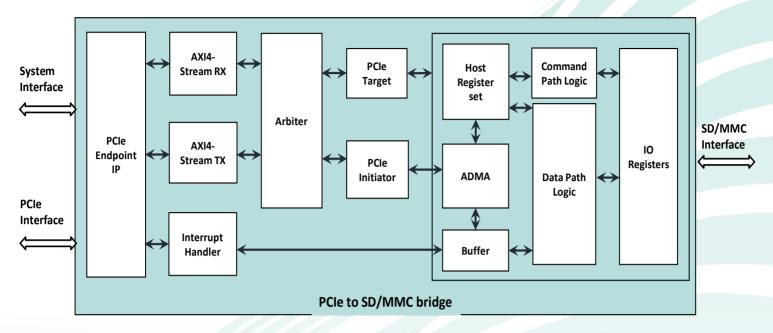

iW-PCle to SD/MMC Bridge is the IP core which converts the PCle to SD or MMC bus interface. The interface towards the SD or MMC card is realized by the SD or MMC protocol implemented in the controller.

# **Applications**

- Used as Bridge between SD/MMC and PCIe.

- End application includes Consumer, Industrial, Automotive, Computer & Storage

## **Highlights**

- Compliant with SD Host

Controller Standard

Specification Version 2.0

- Compliant with SD Physical

Layer Specification Version

2.0

- Compliant with eMMC specification version 5.1

- Supports Gen1 x1 PCle link

### **Features**

- Compliant with SD Host Controller Standard Specification

Version 2.0

- Compliant with SD Physical Layer Specification Version 2.0

- Compliant with eMMC Specification Version 5.1

- Supports 1-bit,4-bit SD/eMMC modes and 8-bit eMMC modes.

- Supports SD Card Detection input pin

- Supports SD Card Write Protection input pin

- Supports programmable clock frequency generation to the SD/eMMC card.

- Supports Interrupt and ADMA2 transfer mode of operation.

- Individual 2Kbyte data buffer for read and write.

- Cyclic Redundancy Check (CRC) for command and data.

- Supports timeout monitoring for response, data, CRC token & busy.

- Supports a maximum block length of 2K-byte.

- Supports both single block and multi block data transfer.

- Supports power ON/OFF control to SD/eMMC card.

- Supports Gen1 x1 PCle link for host processor interface

# iW PCIe to SD/MMC Bridge block diagram

### **Deliverables**

- RTL source code or Netlist

- IP example design

- IP datasheet

- Integration Manual

- Linux driver reference

### **Licensing Options**

- Non-Transferable: Single Project/Product Netlist License Single Site or Multi Site

- Non-Transferable: Multi Project /Product Netlist License Single Site or Multi Site

- Non-Transferable: Single Project/Product RTL Source Code License Single Site or Multi Site

- Non-Transferable: Multi Project/Product RTL Source Code License Single Site or Multi Site

### **Technical Support**

iWave provides comprehensive support during your system integration & validation.

- The Client may open a new support incident by emailing to a technical support engineer

- iWave's response time shall be within 24 hours of the initial call, with the details of the action plan to resolve

- Support assistance shall be delivered by telephone, email and/or remote assistance via a web meeting

- iWave shall provide remote debugging support irrespective of the time zone/ region

iWave Systems, a leading FPGA design house enhances your design productivity by providing an extensive suite of proven, optimized and easy-to-use FPGA IP Cores along with reference designs to complement and quicken your applications development. Our extensive suite of IP Cores covers all key markets and applications. Along with the rich set of FPGA IP cores, iWave offers custom FPGA designs tailored to meet the client specifications which includes RTL Design, Integration of iWave's or 3rd Party IP Cores on our FPGA SOMs with Carrier Card/ Custom Hardware/ Off -the-Shelf Evaluation Kits to provide end-to-end solutions targeting Low-Power, High-Performance and Optimized Designs

iW PCIe to SD/MMC Bridge Controller FPGA IP

The IP can be ordered online from the iWave Website https://www.iwavesystems.com/product/pcie-to-sd-mmc-bridge/ Or from our Local Partners in your region http://www.iwavesystems.com/about-us/business-partner.html

#### INDIA

iWave Systems Tech. Pvt. Ltd., 7/B, 29<sup>th</sup> Main, BTM Layout 2<sup>nd</sup> Stage, Bangalore-560076 Email: mktg@iwavesystems.com

### **JAPAN**

iWave Japan, Inc. 8F-B, Kannai Sumiyoshi Building, 3-29, Sumiyoshi-cho, Naka-ku, Yokohama, Kanagawa, Japan. mktg@iwavesystems.com

#### FUROPE

International Sales & Marketing Europe Venkelbaan 55 2908KE Capelle aan den Ijssel The Netherlands info@iwavesystems.eu

### **USA**

iWave USA 1692 Westmont Ave., Campbell, CA95008 USA info@iwavesystems.us